等长是PCB设计的时候经常遇到的问题。存储芯片总线要等长,差分信号要等长。什么时候需要做等长,等长约束条件是什么呢?

首先,等长的作用。由于信号在PCB走线上存在延时,正比于信号线的长度。假设PCB上有两个完全相同的信号,但是布线长度不同。那么发端完全相同的信号在接收端就会由于延时的差异造成两个信号相位的不同。不相关的信号布线差异都不会引起问题。但是如果两根信号有时序要求,那么信号延时就可能造成信号错误。所以有时序要求的信号就会有等长要求。

例如差分信号,两根差分线上的信号是相位完全相反,如果不等长就会造成信号相位偏差,很容易造成错误。尤其是差分信号一般信号幅度都不高,更容易引起问题。所以差分信号的等长约束一般都比较严格,基本会要求在等长正负50mil以内甚至更小。

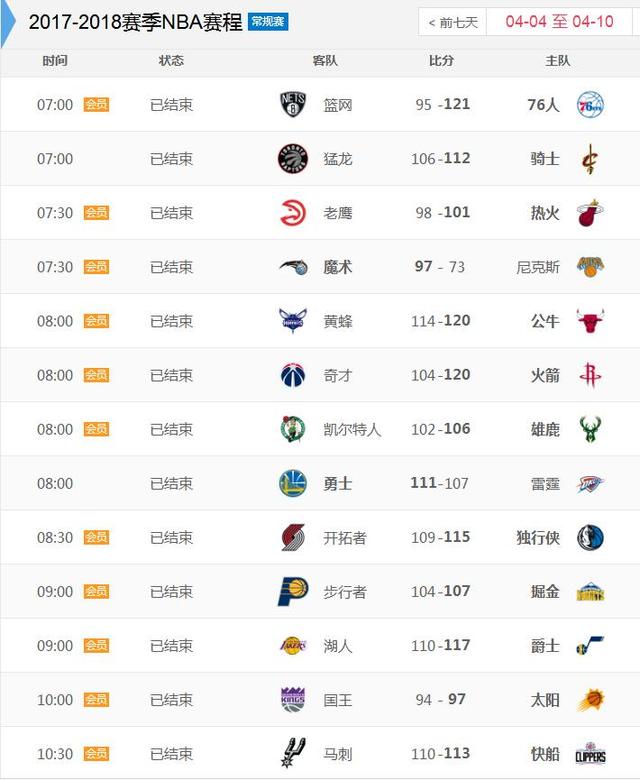

经常看到的还有内存颗粒的等长要求。有些约束说DDR2的等长要求数据线时钟线等长控制在正负50mil,地址线等长控制在正负100mil等等。实际画图的时候可能一个小的弯角就能差出几十个mil。其实这些约束条件比较苛刻,是为了满足绝大部分应用的需要。在我们每一个具体设计当中,可以根据芯片具体要求和运行速率的不同放宽约束条件,同样能满足要求,降低PCB设计复杂度。只要清楚PCB板上走线延时,表层走线大约140ps/inch,内层走线大约166ps/inch,再根据芯片运行速度和信号上升时间保持时间,推算出具体等长要求就可以了。

![欧洲杯开球晚会列强驻华代表齐聚奥地利使馆[组图]_图片中心_中国网](https://0571gr6.com/zb_users/upload/2024/05/202405021714631500579102.jpg)

![[数据]欧洲杯各队缺失球员数据整合(WE2008/PES2008) - 实况足球 [PS4/X1/PC] - A9VG电玩部落论坛 - Powered by Discuz!](https://0571gr6.com/zb_users/upload/2024/04/202404091712635522465779.jpg)

![[辣评欧洲杯]预料之中的平局-搜狐](https://0571gr6.com/zb_users/upload/2024/04/202404061712376813143227.jpg)

![伦敦奥运会2012游戏_伦敦奥运会2012游戏完整版下载[体育竞技]-下载之家](https://0571gr6.com/zb_users/upload/2024/03/202403301711772125138071.jpg)

![[1]林卡等:《城市国际化指标体系研究》](https://0571gr6.com/zb_users/upload/2024/03/202403151710516739333927.gif)

![office 发音:[fs]意思:n. 办公室](https://0571gr6.com/zb_users/upload/2024/03/202403081709883101379697.jpg)

![回复[书库]查看:适合出国党的19个在线英文书库](https://0571gr6.com/zb_users/upload/2024/03/202403051709577441172718.gif)

网友评论

最新评论